Main Takeaway

电学预演——对模电、数电以及如何从0到1设计一台计算机进行概览。(之前我上过计算机基础所以对一些概念有所了解并未全都详细记录,而是凭借自己的理解说出来)

特别感谢B站Ele实验室的视频!建议直接跳转到References观看链接视频,相信你和我一样能受益匪浅。

模电

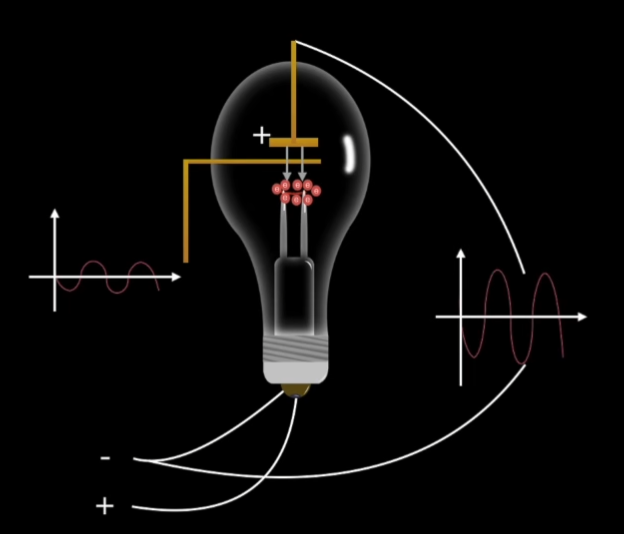

电子管

缺点:体型大,做不了微型化;功耗高,容易出故障

优点:有极强的抗干扰性,大功率低噪声

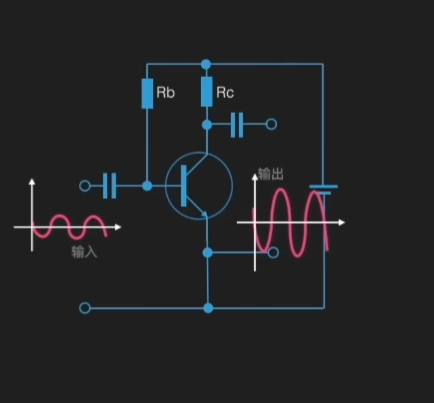

Tips:三极管的重要特性:信号放大!

晶体管

纯净的半导体:本征半导体

加磷P:N型半导体(电中性),易失去电子

加硼B:P型半导体

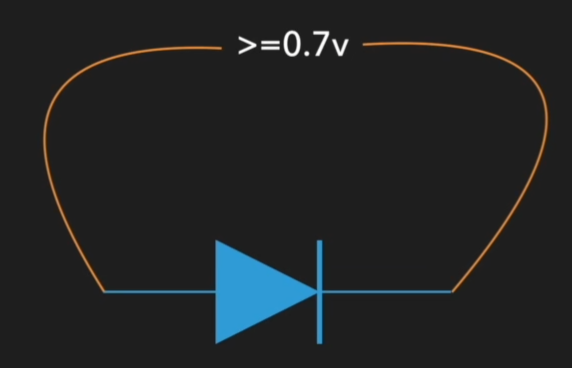

PN结——amazing!:

先是扩散运动:电子从N流向P

因为电荷不均匀产生电场阻碍电子的流向有了漂移运动:电子从P流向N

最后达到动态平衡

Tips:电学的大厦感觉就是在PN结的基础上搭建而成的

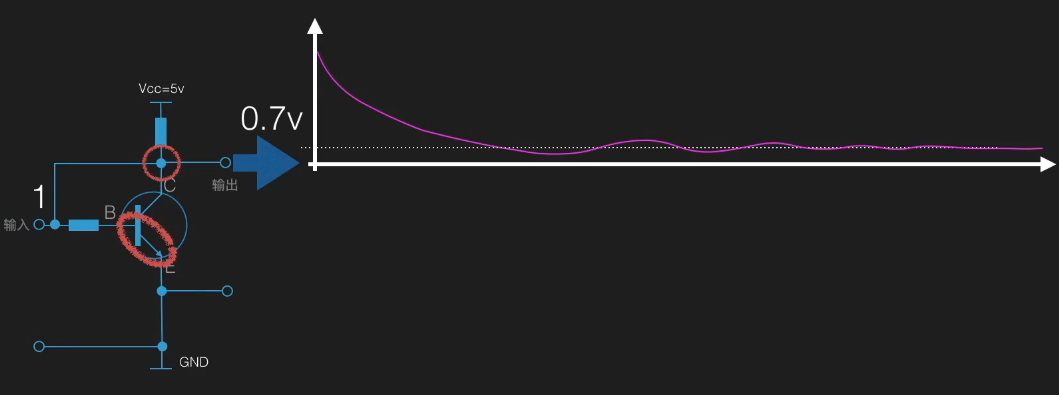

导通电压一般为0.7V,小于导通电压称为截止;

Tips:三极管不仅有截止的状态还有饱和,详情可查看三极管的特性曲线

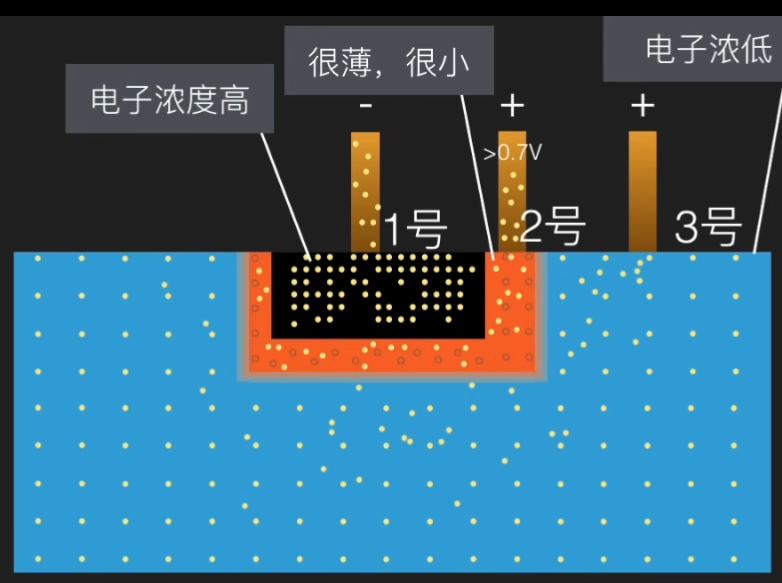

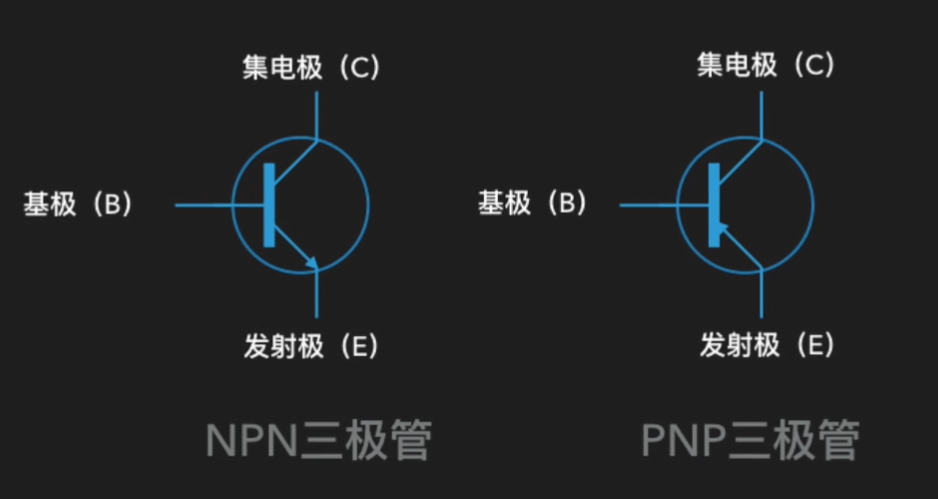

晶体三极管原理:1号与2号之间导通电压大于0.7V,使1 2之间的PN结形成通路,涌入2号的电子很多会扩散到3号,很快就被3号收集起来了,2号很薄消耗电子能力有限电流小,3号空间大电流一般较大,2号也能以较小的变化改变3号较大的变化。

1号发射极:发射电子

2号基极:像阀门一样操作着原始信号

3号集电极:收集电子

Tips:具体分析见视频:Rb Rc都是为了分压,PN结导通只需要0.7V即可,电容可以导通不同方向的电流(取代二极管),利用三极管的特性方法输入的信号。

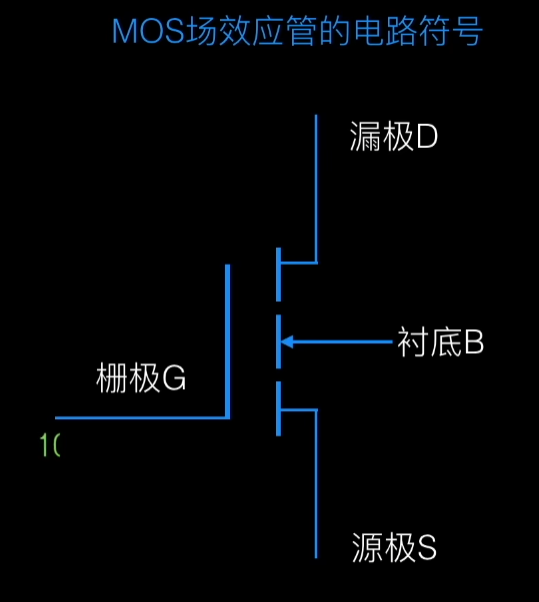

场效应管

最为常见的是mos管

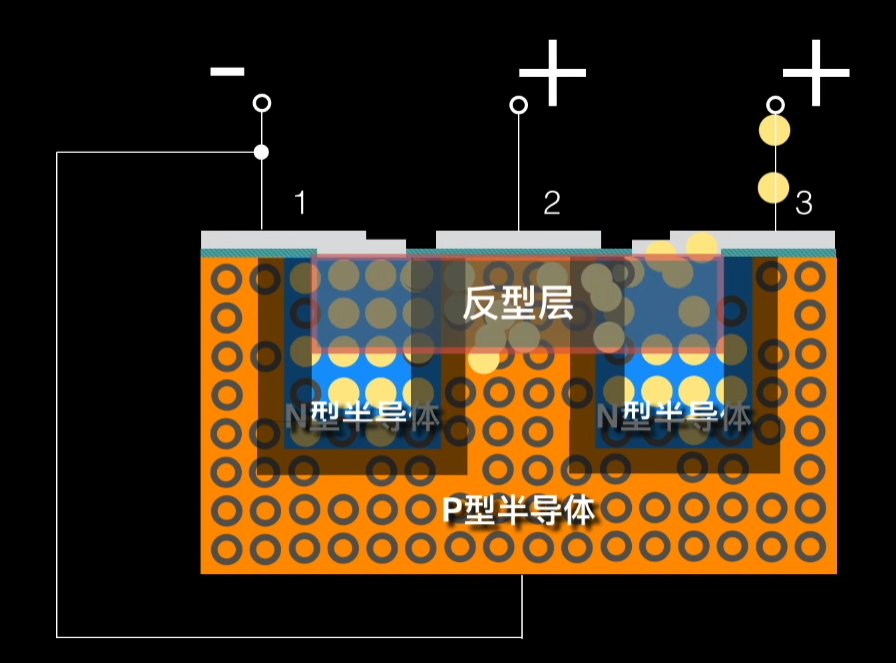

mos管原理:1号和3号与N型半导体直接相连,1号N型半导体导通电子流出到P型半导体,2号电吸引电子在上方形成反型层——该区域的电子比1、3N型半导体的电子都多,于是电子进入3号的N型半导体从3号流出(1号不会流出因为1是负极强行提供电子)

1源极:提供电子

2栅极:用0和1来控制,像个栅栏一样

3漏极:收集电子(通过反型层的导电沟道捡漏)

数电

执行逻辑运算的电路——门电路,数电就是把一个个门电路结合起来实现复杂的逻辑运算甚至算术运算

GND接地:消除不同系统间因为电位的相对性而导致的电压标准的混乱

在数电中我们只管有电还是没电即1和0

Tips:1,0都有一个电平范围

门电路符号后面的小圈圈表示将结果取反

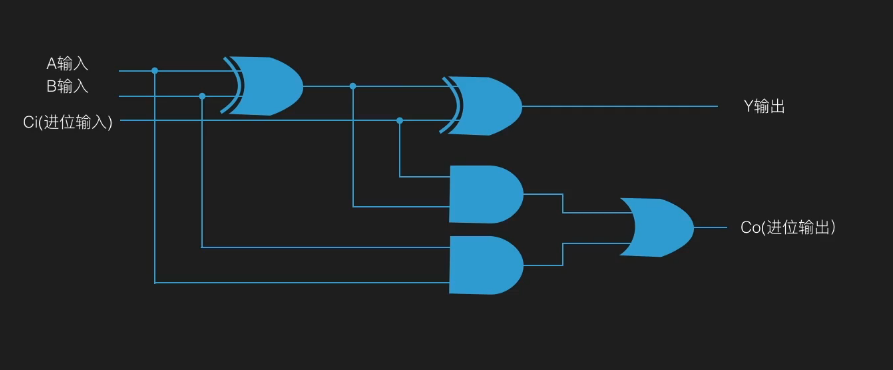

全加器

加减法——补码(各位取反+1)

不接受进位的加法器——半加器,接收进位全加器

能够同时接受并输出仅为的电路单元——全加器(加减都能用)

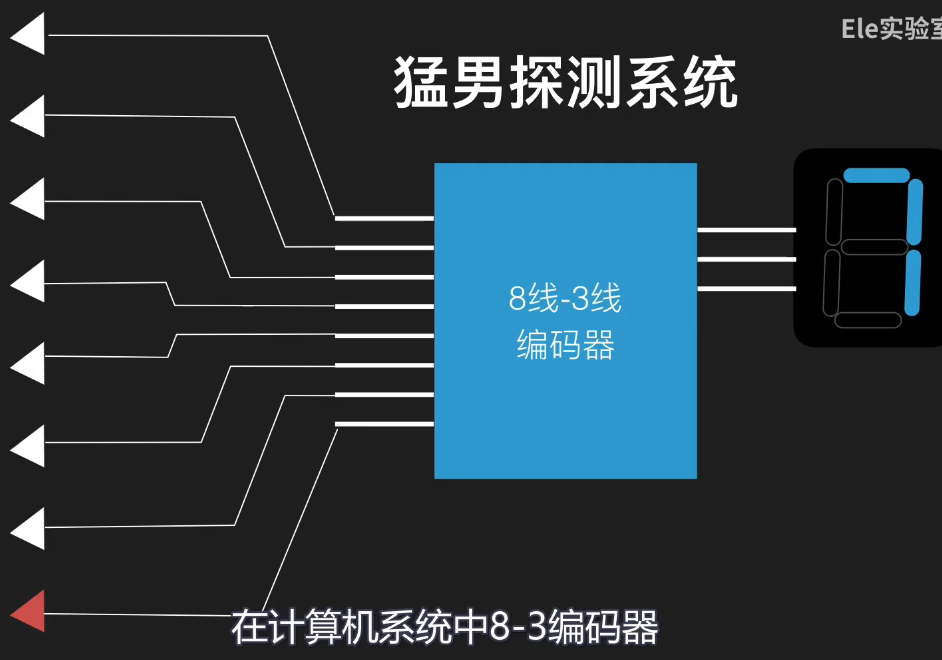

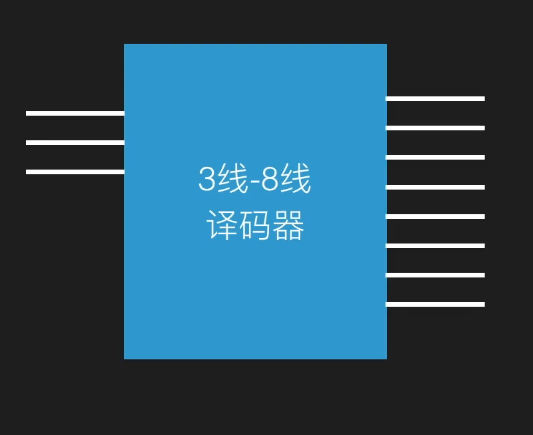

编码器与译码器

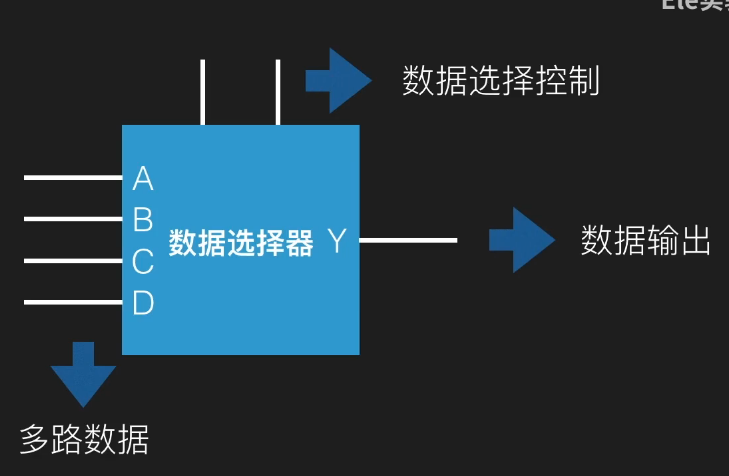

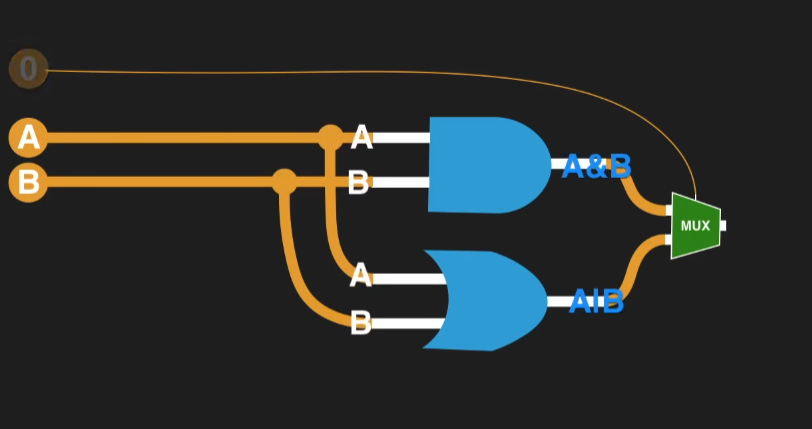

数据选择器

即为多路开关

Notes:电路不会震荡,因为电流响应也需要时间而不是突变。

有两个稳定状态的系统——双稳态系统

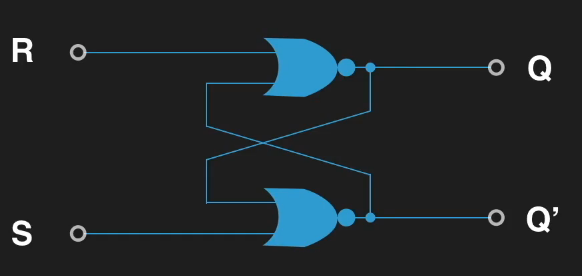

SR锁存器

存储数据(拥有记忆功能)——S置位端,R复位端(置0端)

实际上电路S、R只能一个一个地改变

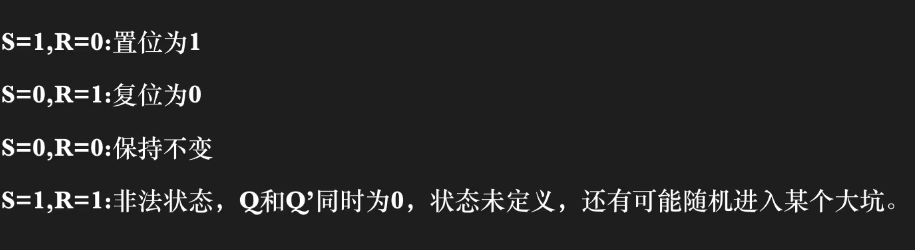

SR触发器

同步触发:CLK=1,输入被锁死,CLK=0,输入被触发,可实现同步(只需要有同一个CLK信号)

CLK——电平触发(电磁干扰不好);脉冲触发比较好

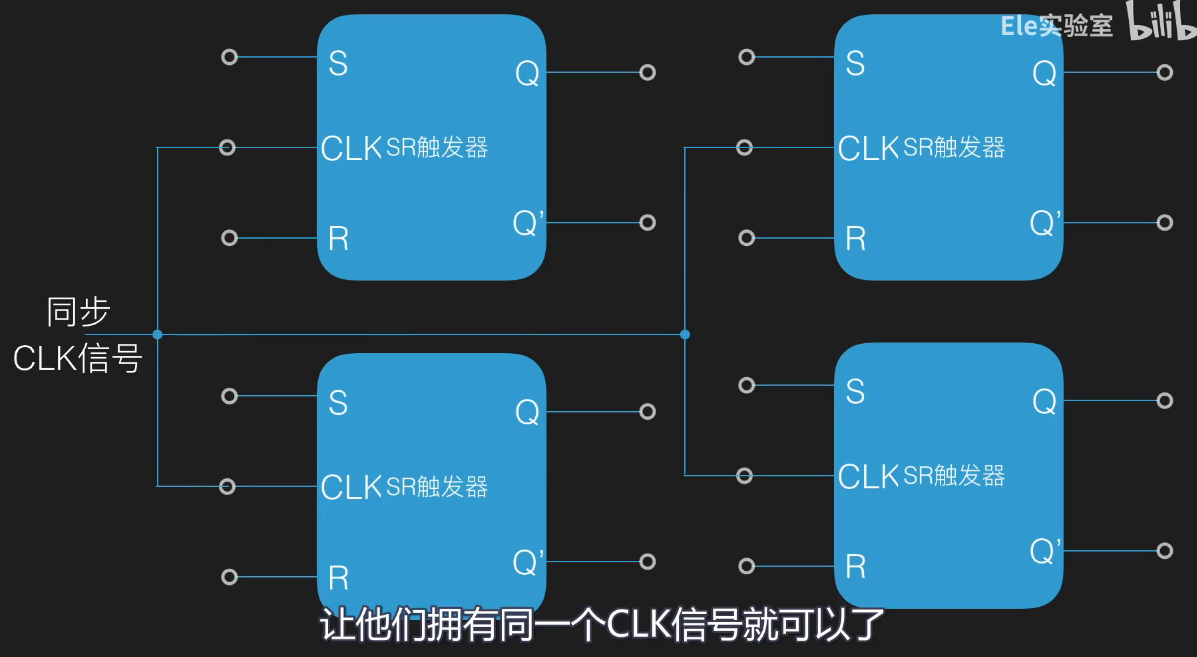

D触发器

用一个非门把S和R地输入合并成一个(原来4种输入变成了3种,1,1这种非法的被删去了)

脉冲触发器由两个电平触发器结合而成(被淘汰)

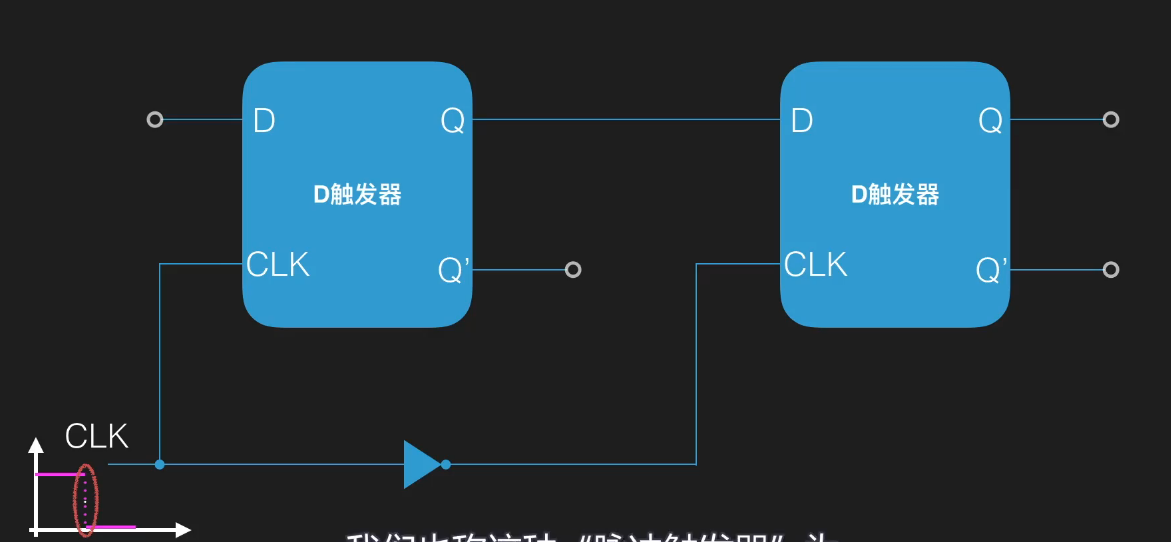

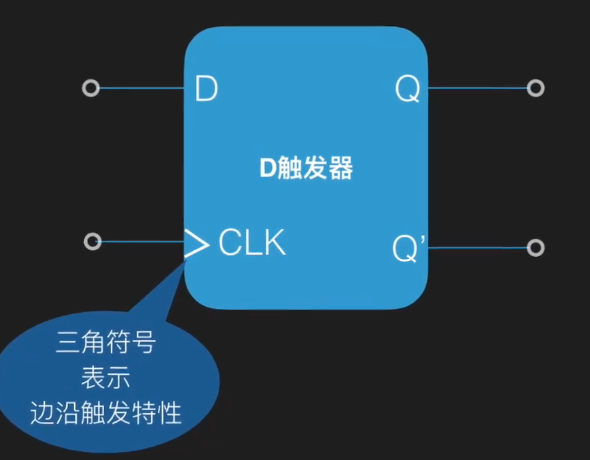

边沿触发器

由两个电平D触发器结合而成

Tips:脉冲触发器由两个电平触发器结合而成(被淘汰)

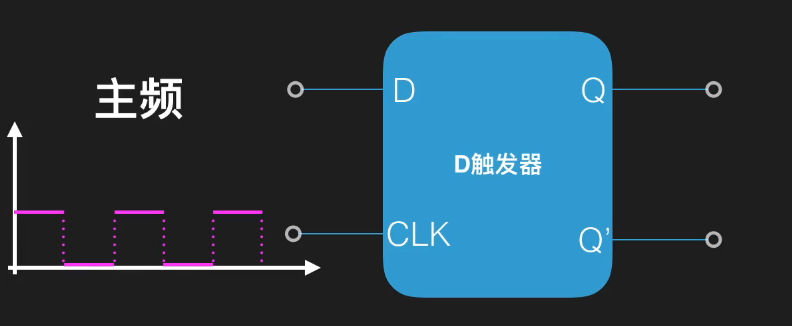

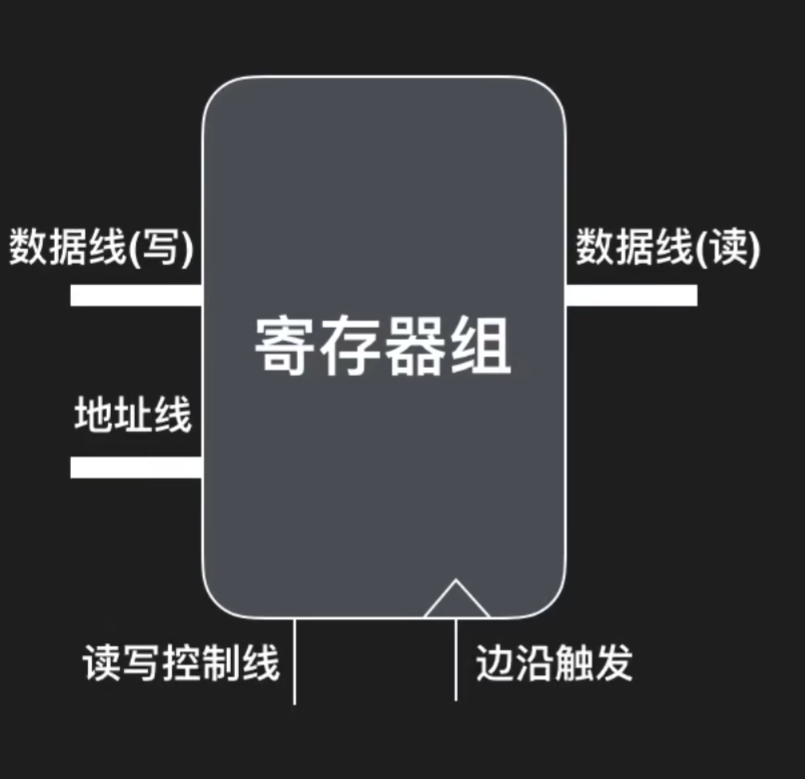

寄存器

寄存器由多个边沿触发器组合而成

拥有记忆了,这种按照脉冲时间序列动作的电路称为时序逻辑电路=组合逻辑电路+具有记忆功能的存储电路

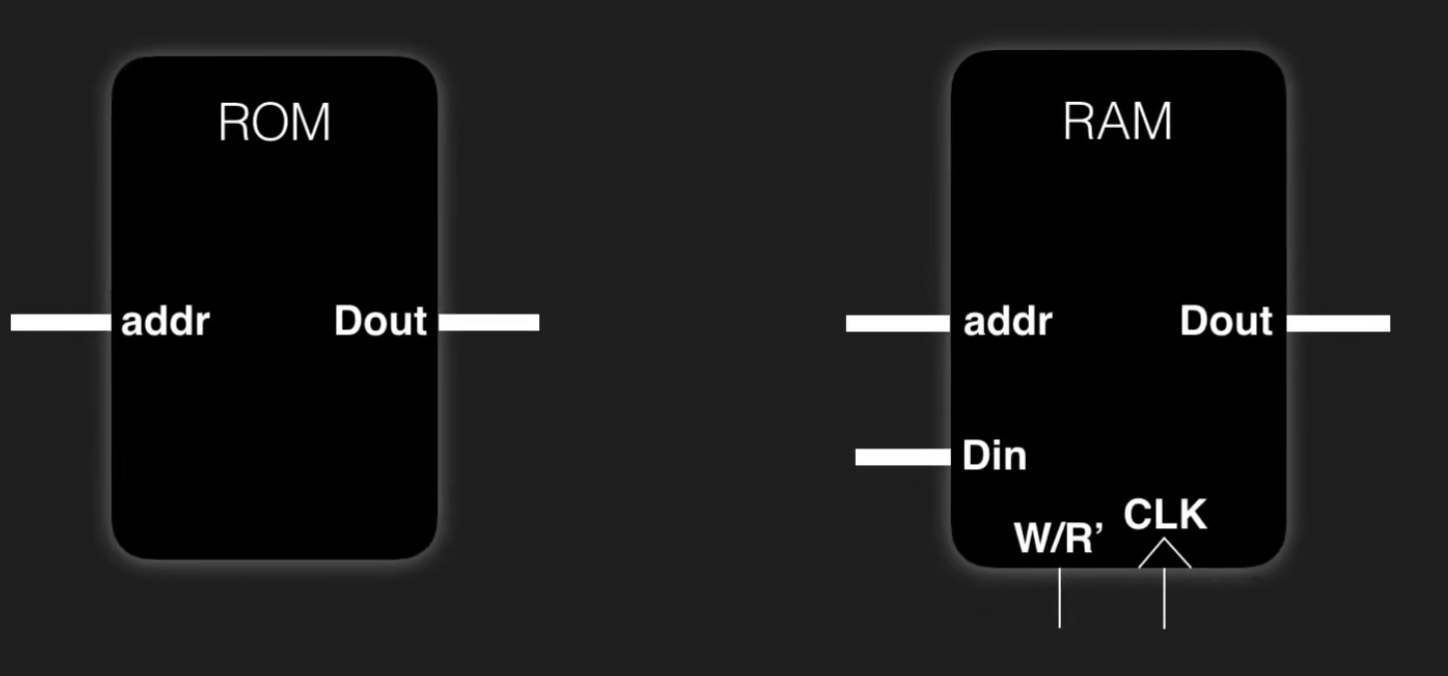

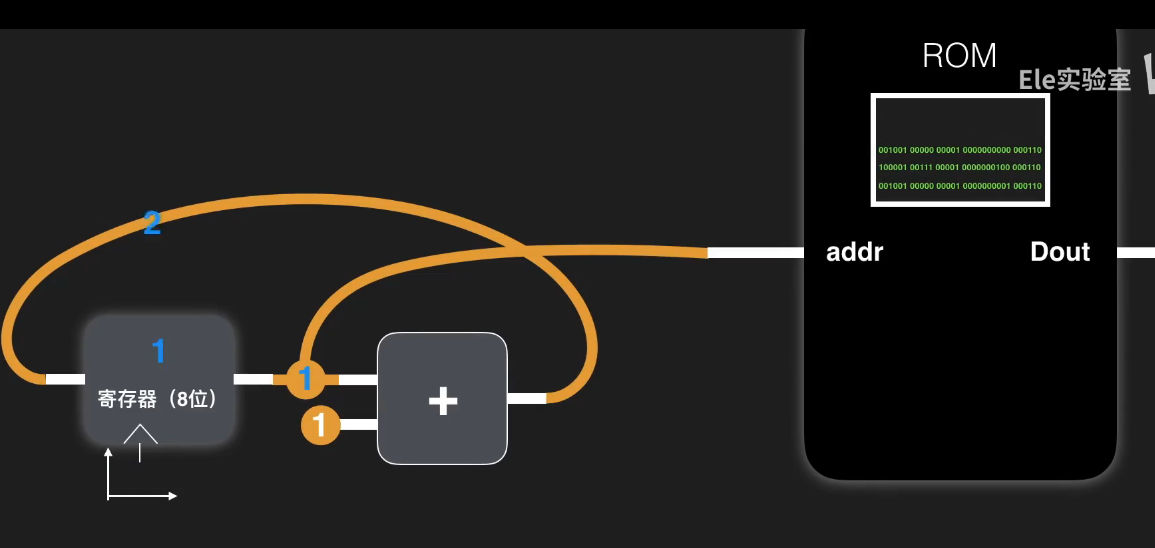

ROM

Read Only Memory,只读已经消失了,flash可读可写

普通ROM——PROM可编程(Programmable ROM)

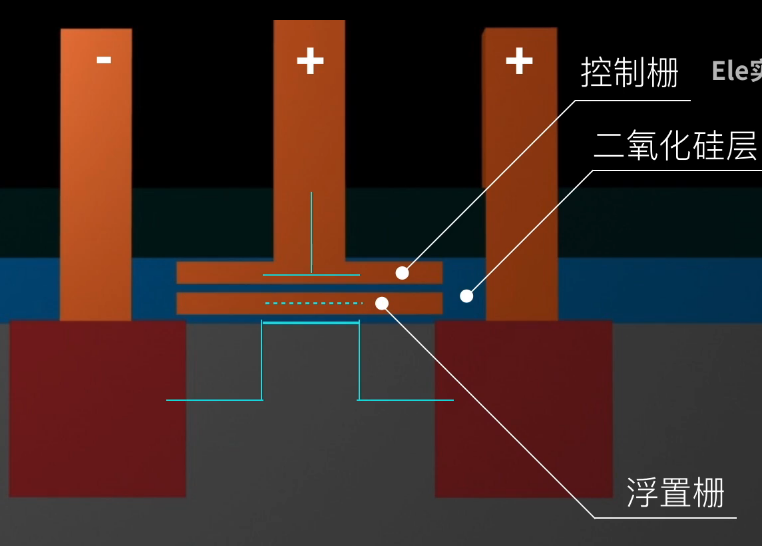

增加浮置栅EPROM(erasable Programmable Read Only Memory)可擦除可编程——EEPROM(量子隧道)——Flash

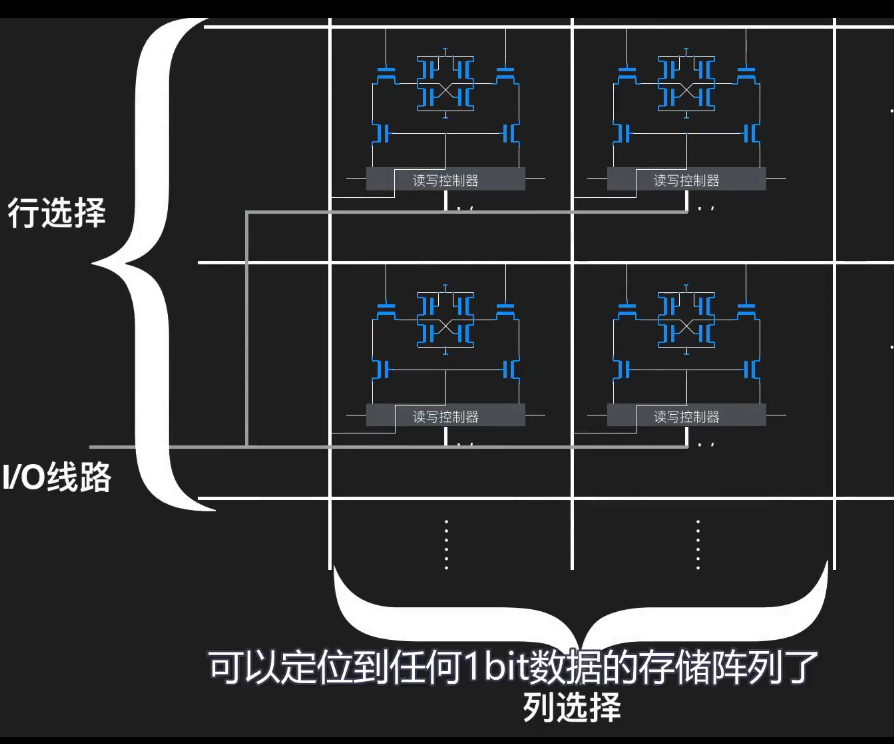

RAM

Random Access Memory,迅速,断电不能保存数据,功耗低

锁存结构:不过较复杂,集成度上不去,用在性能要求更高的buffer中——静态RAM(SRAM)

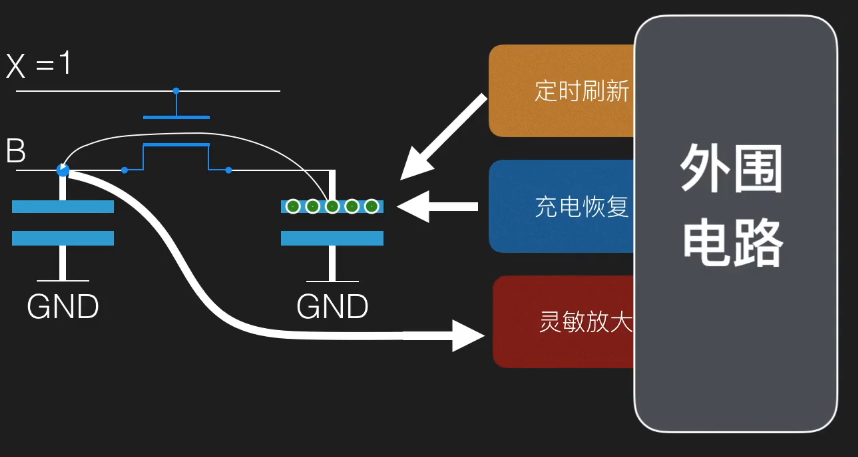

用电容实现存储——需要复杂的外围电路的配合——动态RAM(DRAM)内存就是DRAM

Bonus

DDR(double data rate)——脉冲上升沿、下降沿都可以触发,实现双倍速率

时钟信号同步——SDRAM, DDR SDRAM

设计计算机

冯诺依曼结构,哈佛结构——常见于单片机,MCU中

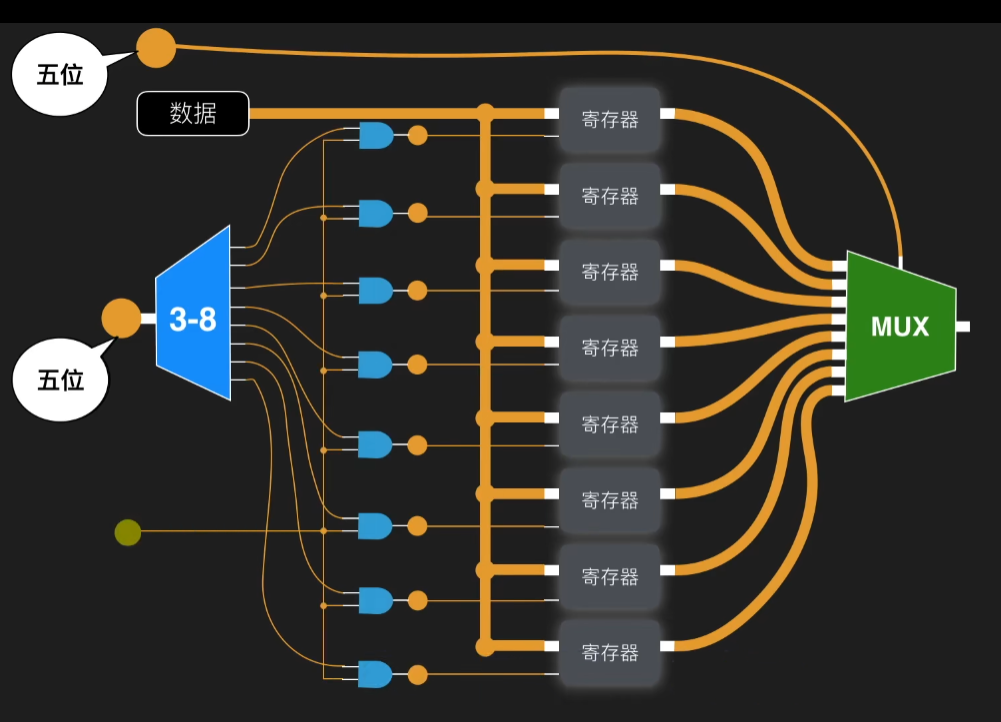

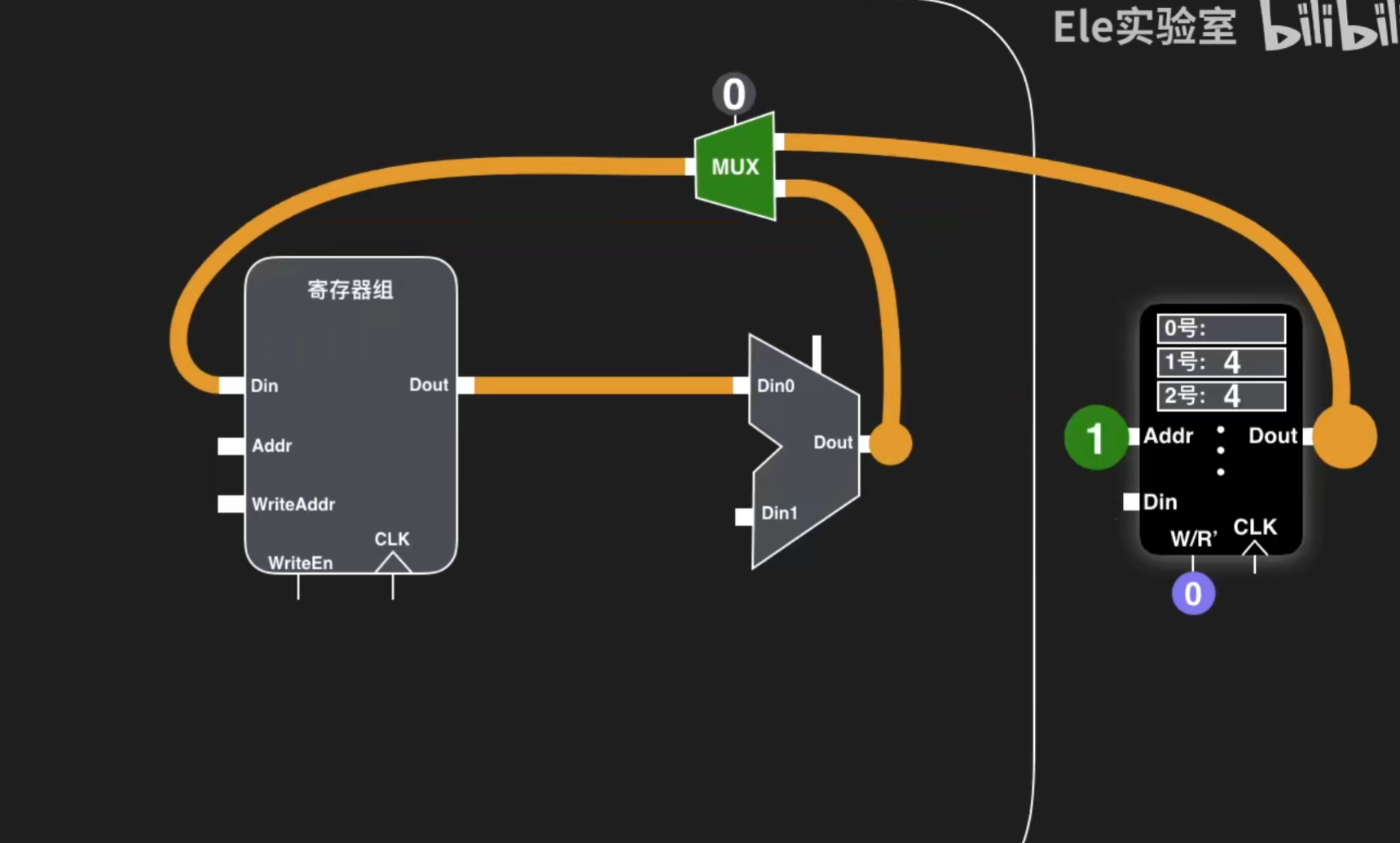

寄存器组

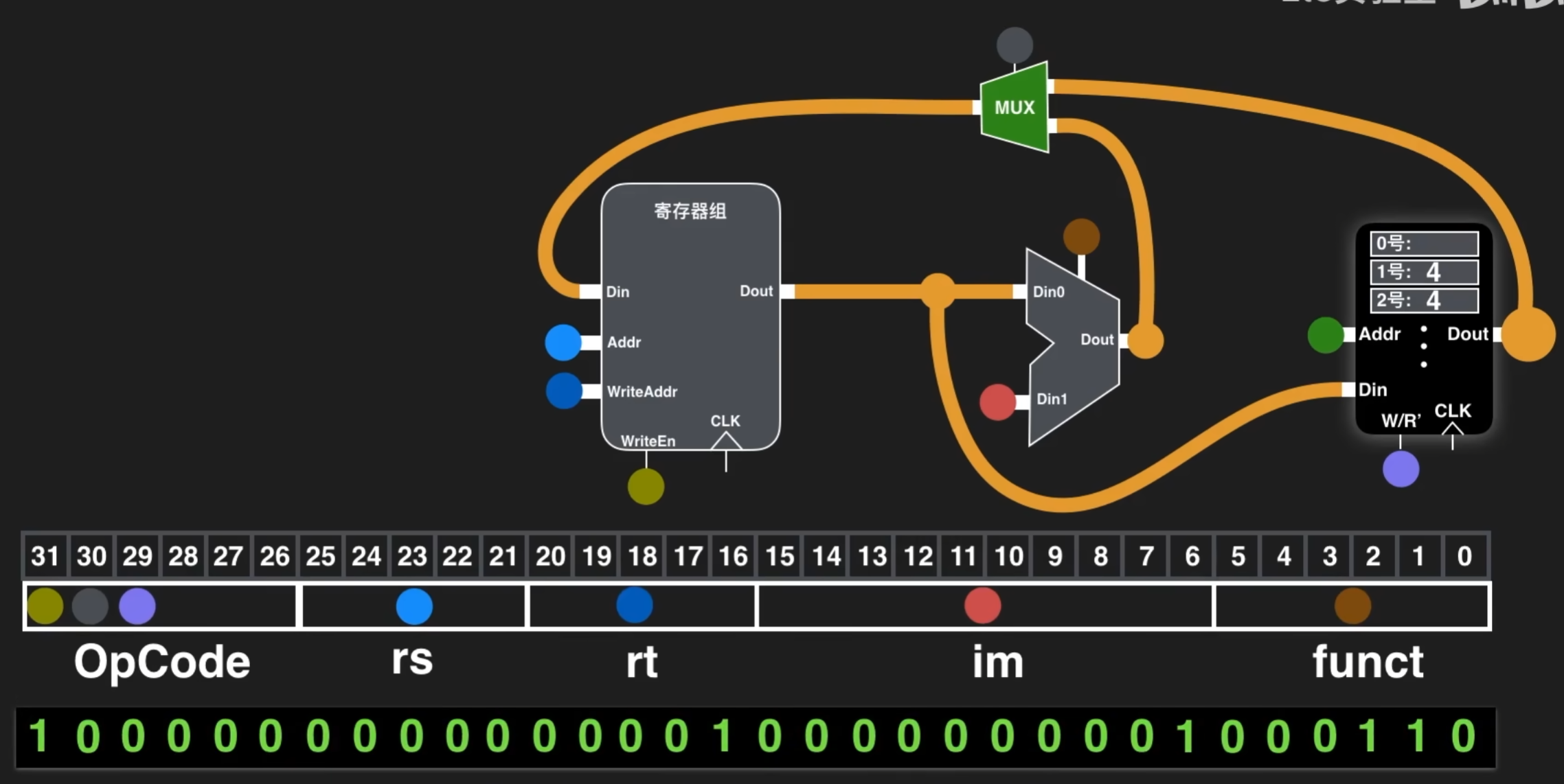

CLK:时钟脉冲,Dout:data out,可随意读取

设计原则:CPU和RAM必须通过寄存器组进行交流

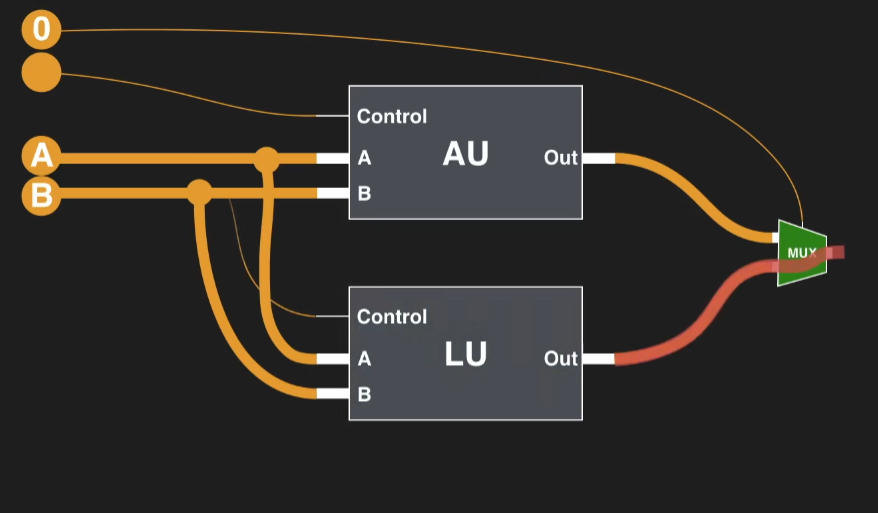

Tips:如果对于输入有不同的输出方式,一般都有一个控制信号来表示选择哪一个模式

运算器

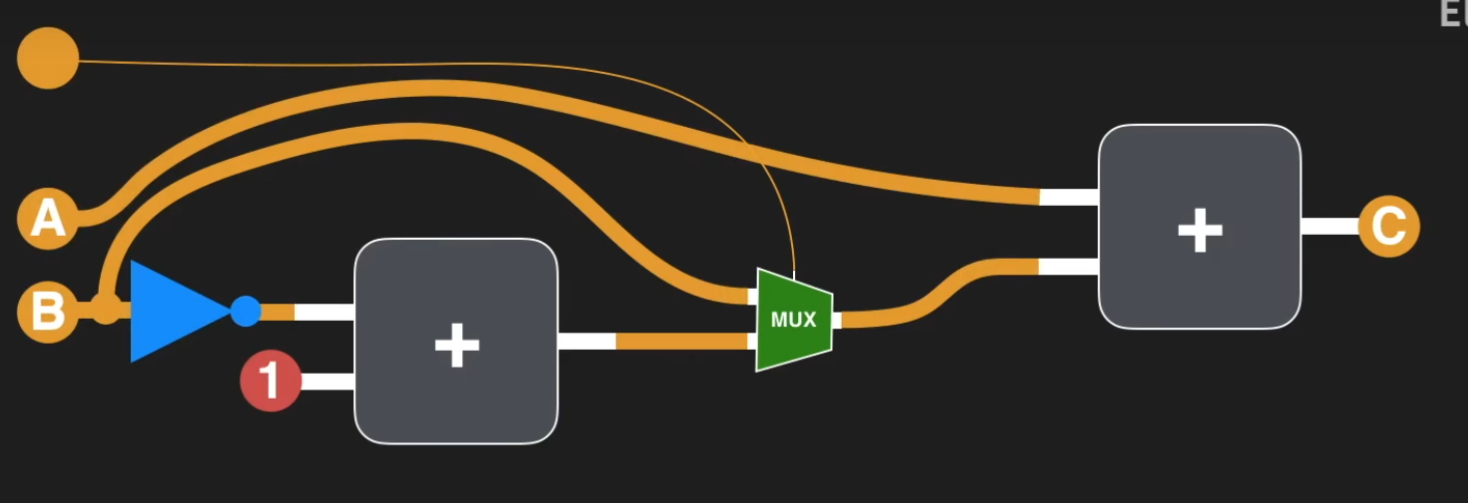

AU

arithmetic unit算术单元

LU

logic unit逻辑单元

ALU

arithmetic and logic unit算术逻辑单元

指令集

汇编器

汇编器就是将汇编语言转化为指令集,汇编语言:把人性化的语言转化为二进制机器指令的工作

一般是先设计汇编再结合电路反推出二进制

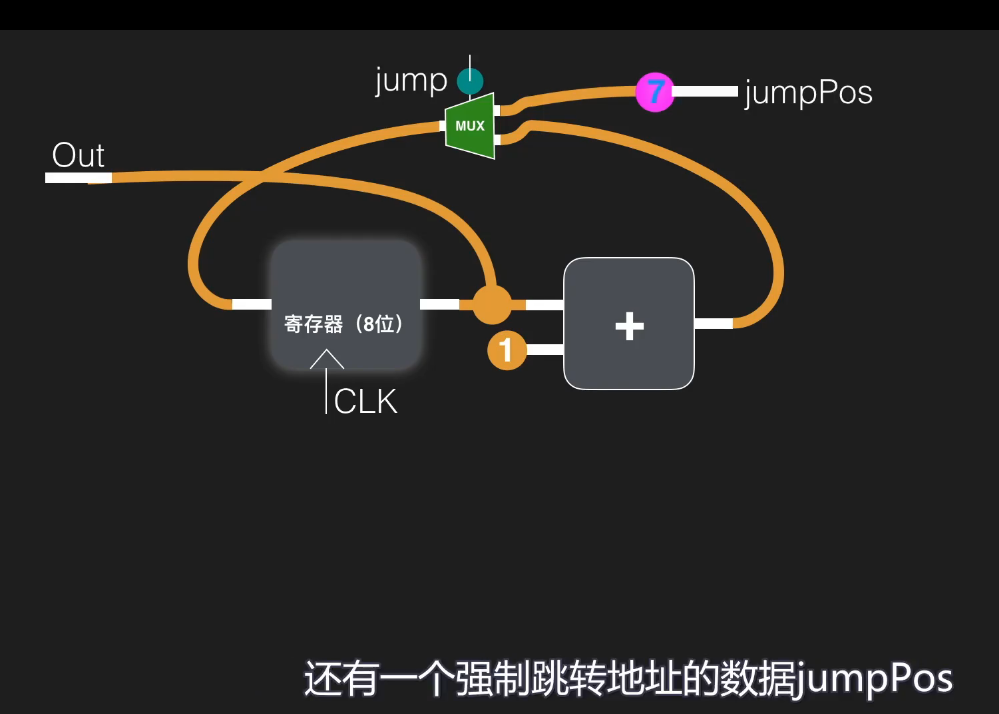

程序计数器

PC(program counter)——CPU的一部分,自动实现指令的依次执行,控制程序顺序

I型指令

J型指令:比如强制跳转地址

Bonus

其他的比如图像的显示——用一条IO口引出即可。

我们需要什么功能,都可以运用我们的智慧改进硬件来达到要求!计算机的设计就是一个不断迭代的过程。

References

- 【编程前你最好了解的基本硬件和计算机基础知识(模拟电路)】https://www.bilibili.com/video/BV1774114798?p=2&vd_source=93bb338120537438ee9180881deab9c1

- 【编程前你最好了解的基本硬件和计算机基础知识(数字电路)】https://www.bilibili.com/video/BV1Hi4y1t7zY?vd_source=93bb338120537438ee9180881deab9c1

- 【从0到1设计一台计算机】https://www.bilibili.com/video/BV1wi4y157D3?vd_source=93bb338120537438ee9180881deab9c1